# **System-Level Programming**

#### 17 $\mu$ C-System Architecture – Peripherals

#### J. Kleinöder, D. Lohmann, V. Sieh, P. Wägemann

Lehrstuhl für Informatik 4 Systemsoftware

Friedrich-Alexander-Universität Erlangen-Nürnberg

Summer Term 2024

http://sys.cs.fau.de/lehre/ss24

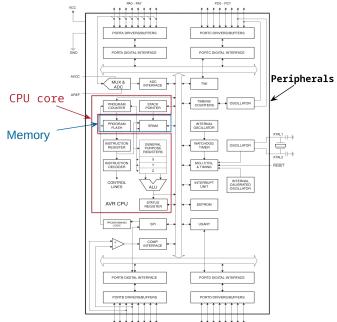

- $\mu$ Controller := processor + memory + peripherals

- In fact, computer system on one chip  $\longrightarrow$  System-on-a-Chip (SoC)

- Often usable without additional external components, like e.g., clock generators and memory → cost-efficient system design

- Main features are (plentiful) contained input/output components (peripherals)

- The distinctions are not fixed: processor  $\longleftrightarrow \mu C \longleftrightarrow SoC$

- AMD64 CPUs also have included timers, memory (cache), ...

- Some  $\mu$ C reach the speed of "big processors"

## Example ATmega32: Block Circuit Diagram

hardware component that is located "outside" of the central unit of a computer

Traditional (PC): keyboard, monitor, ...

$(\mapsto physically "outside")$

In general: hardware functions that are not directly map-

ped into the processor's instruction set

$(\mapsto logically "outside")$

Peripheral components are addressed via I/O registers

Control registers: instructions to control/query state of peri-

pheral is encoded by bit patterns (e.g., DDRD

for ATmega)

Data registers: required for exchange of data

(e.g., PORTD, PIND for ATmega)

Registers are often only available as read-only or write-only

#### Peripheral Devices: Examples

• Selection of typical peripheral devices of a  $\mu$ Controller

| <ul><li>Timer/Counter</li></ul> | Counting registers that are incremented with a defined fre- |

|---------------------------------|-------------------------------------------------------------|

|                                 | quency (timer) or by external signals (counter) and that    |

|                                 | trigger an interrupt at a configurable counting value.      |

- Watchdog timer Timer that has to be written to regularly otherwise a RE-SET is triggered ("dead man's button").

- (A)synchronous

serial interface

Component for serial (bit-wise) exchange of data with a synchronous (e. g., RS-232) or asynchronous (e. g., I<sup>2</sup>C) protocol.

- A/D converter Component for onetime/continuous discretization of voltage values (e. g.,  $0-5V \mapsto 10$ -bit integer).

- PWM generators

Component for generating pulse-width-modulated signals, pseudo-analog (D/A) output.

- Ports Groups of usually 8 ports which can be set to GND or Vcc and whose states can be monitored.  $\hookrightarrow$  17–16

- Bus systems SPI, RS-232, CAN, Ethernet, MLI, I<sup>2</sup>C, ...

Memory-mapped: Registers are integrated in address space; access with memory instructions of the processor (load, store)

Port-based: Registers are organized in a separate I/O ad-(x86-based PCs)

Registers are organized in a separate I/O address space; access with special in- and out-

instructions

Registers are integrated in address space; ac-Memory-mapped:

cess with memory instructions of the processor (most  $\mu$ C)

(load, store)

Port-based: Registers are organized in a separate I/O ad-

(x86-based PCs) dress space; access with special in- and out-

instructions

Addresses of the registers are listed in the hardware's documentation

| Address     | Name    | Bit 7         | Bit 6                                | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Page |

|-------------|---------|---------------|--------------------------------------|--------|--------|--------|--------|--------|--------|------|

| \$3F (\$5F) | SREG    | - 1           | T                                    | Н      | S      | V      | N      | Z      | С      | 8    |

| \$3E (\$5E) | SPH     | -             | -                                    | -      | -      | SP11   | SP10   | SP9    | SP8    | 11   |

| \$3D (\$5D) | SPL     | SP7           | SP6                                  | SP5    | SP4    | SP3    | SP2    | SP1    | SP0    | 11   |

| \$3C (\$5C) | OCR0    | Timer/Counter | mer/Counter0 Output Compare Register |        |        |        |        |        |        | 86   |

|             |         |               |                                      |        |        |        |        |        |        |      |

| \$12 (\$32) | PORTD ) | PORTD7        | PORTD6                               | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | 67   |

| \$11 (\$31) | DDRD    | DDD7          | DDD6                                 | DDD5   | DDD4   | DDD3   | DDD2   | DDD1   | DDD0   | 67   |

| \$10 (\$30) | PIND    | PIND7         | PIND6                                | PIND5  | PIND4  | PIND3  | PIND2  | PIND1  | PIND0  | 68   |

[1]

$\blacksquare$  DDRx

Data Direction Register: Determines for every pin i whether it is used as input (bit i=0) or output (bit i=1).

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DDRD7 | DDRD6 | DDRD5 | DDRD4 | DDRD3 | DDRD2 | DDRD1 | DDRD0 |

| R/W   |

PORTX

**Data Register:** If pin i is configured to be an output, bit i determines the voltage level (0=GND sink, 1=Vcc source). If pin i is configured to be an input, bit i activates the internal pull-up resistor (1=active).

| ,      | o .    | 3      | -      | 3      | -      |        | 0      |   |

|--------|--------|--------|--------|--------|--------|--------|--------|---|

| PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | 1 |

| R/W    |   |

■ PINX

**Input** Register: Bit i represents the voltage level at pin i (1=high, 0=low), independent of the data direction of the register.

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PIND7 | PIND6 | PIND5 | PIND4 | PIND3 | PIND2 | PIND1 | PIND0 |

| R/W   |

Examples:  $\hookrightarrow$  3–8 and  $\hookrightarrow$  3–12

[1]

- $\blacksquare$  register  $\mapsto$  memory  $\mapsto$  variable

- all C operators are directly available (e.g., PORTD++)

- Syntactically, preprocessor macros simplify the access:

```

#define PORTD (*(volatile uint8_t *) 0x12

```

- Memory-mapped registers enable convenient access

- $\blacksquare$  register  $\mapsto$  memory  $\mapsto$  variable

- all C operators are directly available (e.g., PORTD++)

- Syntactically, preprocessor macros simplify the access:

```

#define PORTD (*(volatile uint8_t *)

address: int

```

- Memory-mapped registers enable convenient access

- lacktriangleright register  $\mapsto$  memory  $\mapsto$  variable

- all C operators are directly available (e.g., PORTD++)

- Syntactically, preprocessor macros simplify the access:

```

#define PORTD (*(volatile uint8_t *) 0x12 ) address: int address: volatile uint8_t *(cast \hookrightarrow \frac{7-32}{7-32})

```

- - Memory-mapped registers enable convenient access

- $\blacksquare$  register  $\mapsto$  memory  $\mapsto$  variable

- all C operators are directly available (e.g., PORTD++)

- Syntactically, preprocessor macros simplify the access:

```

#define PORTD (*(volatile uint8_t *)

address: volatile uint8_t *(cast → 7-32)

value: volatile uint8_t (dereferencing → 13-5)

```

- Memory-mapped registers enable convenient access

- $\blacksquare$  register  $\mapsto$  memory  $\mapsto$  variable

- all C operators are directly available (e.g., PORTD++)

- Syntactically, preprocessor macros simplify the access:

```

#define PORTD (*(volatile uint8_t *)

address: int

address: volatile uint8_t *(cast → 7-32)

value: volatile uint8_t (dereferencing → 13-5)

```

Therefore PORTD is syntacticallyequivalent to a volatile uint8 t-variable that is stored at address 0x12

- Memory-mapped registers enable convenient access

- register  $\mapsto$  memory  $\mapsto$  variable

- all C operators are directly available (e.g., PORTD++)

- Syntactically, preprocessor macros simplify the access:

```

#define PORTD (*(volatile uint8_t *) 0x12 address: int address: volatile uint8_t *(cast \hookrightarrow 7-32) value: volatile uint8_t (dereferencing \hookrightarrow 13-5)

```

Therefore PORTD is syntactically-equivalent to a volatile uint8\_t-variable that is stored at address 0x12.

Example

- This change in contrast to the assumption of the compiler

- Access to variables only takes place by the currently executed function

- → Variables are temporarily stored in registers

- Peripheral devices operate concurrently to the software

- → Value in hardware registers can change anytime

- This change in contrast to the assumption of the compiler

- Access to variables only takes place by the currently executed function

```

→ Variables are temporarily stored in registers

```

```

// C code

// Resulting assembly code

#define PIND \

(*(uint8_t*) 0x10)

foo:

void foo(void) {

lds

r24, 0x0010 // PIND->r24

r24, 1 // test bit 1

sbrc

if (! (PIND & 0x2)) {

rjmp L1

// button0 pressed

// button0 pressed

L1:

sbrc r24, 2 // test bit 2

if (! (PIND & 0x4)) {

rjmp L2

// button 1 pressed

L2:

ret

```

→ Value in hardware registers can change anytime

- This change in contrast to the assumption of the compiler

- Access to variables only takes place by the currently executed function

```

→ Variables are temporarily stored in registers

```

```

// C code

// Resulting assembly code

#define PIND \

(*(uint8_t*) 0x10)

foo:

void foo(void) {

lds

r24, 0x0010 // PIND->r24

r24, 1 // test bit 1

sbrc

if (! (PIND & 0x2)) {

rimp L1

// button0 pressed

// button0 pressed

L1:

sbrc r24. 2 // test bit 2

if (! (PIND & 0x4)) {

rjmp

PIND is not again loaded

// button 1 pressed

from memory. The com-

L2:

piler assumes the value in

ret

r24 to still be accurate

```

- Compiler minimizes the time, the variable is held in registers

- → Value is read immediately before use

- → Value is written *immediately after* modification

- Compiler minimizes the time, the variable is held in registers

- → Value is read immediately before use

- → Value is written *immediately after* modification

```

// C code

// Resulting assembly code

#define PIND \

(*(volatile uint8_t*) 0x10)

foo:

void foo(void) {

lds r24, 0x0010 // PIND->r24

sbrc r24. 1 // test bit 1

if (! (PIND & 0x2)) {

rjmp L1

// button0 pressed

// button0 pressed

11:

lds r24, 0x0010 // PIND->r24

if (! (PIND & 0x4)) {

sbrc r24. 2 // test bit 2

rjmp L2

// button 1 pressed

PTND is declared as

volatile. It is therefore

L2:

loaded from memory befo-

ret

re each test

```

17-MC-Peripherie

volatile can be used to implement active waiting:

```

// C code

// Resulting assembly code

wait:

void wait(void) {

for(uint16_t i=0; i<0xffff; i++);</pre>

// compiler has optimized

// "unneeded" loop

ret

```

- volatile semantics prevent many code optimizations; in particular the removal of apparently unnecessary code

- volatile can be used to implement active waiting:

```

// C code

void wait(void) {

for(uint16_t i=0; i<0xffff; i++);

}

volatile!

// Resulting assembly code

wait:

// compiler has optimized

// "unneeded" loop

ret</pre>

```

- volatile semantics prevent many code optimizations; in particular the removal of apparently unnecessary code

- volatile can be used to implement active waiting:

```

// C code

// Resulting assembly code

void wait(void) {

wait:

for(uint16_t i=0; i<0xffff; i++);</pre>

// compiler has optimized

// "unneeded" loop

ret

yolatile!

```

#### **Attention:** volatile $\mapsto$ \$\$\$

System-Level Programming (ST 24)

The use of volatile causes considerable runtime penalties

- Values cannot be stored in registers any longer

- Most code optimizations cannot be performed any longer

Use volatile only in justified scenarios Rule:

- **Port** := group of (usually 8) digital inputs/outputs

- Digital output: bit value  $\mapsto$  voltage level at  $\mu$ C pin

- Digital input: voltage level at  $\mu$ C pin  $\mapsto$  bit value

- External interrupt: voltage level at  $\mu$ C pin  $\mapsto$  bit value (on voltage change)  $\rightsquigarrow$  processor executes interrupt program

- This function is usually configurable per pin

- Input

- Output

- External interrupt (only for some inputs)

- Alternative functions (pin used by another device)

17-MC-Peripherie

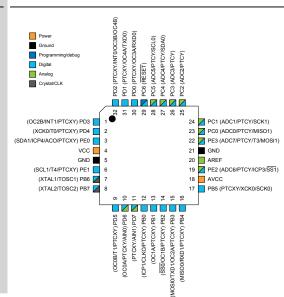

## Example ATmega328PB: Port/Pin Assignment

For reasons of cost efficiency nearly every pin is assigned twice. The configuration of the respective functionality takes place in software.

E. g., pins 23-24 are configured as ADCs at the SPiCBoard to connect potentiometer and photo sensor.

Those pins are therefore not available for PORTC

[1] ATmega328PB 8-bit AVR Microcontroller with 32K Bytes In-System Programmable Flash. Atmel Corporation. Okt. 2015.