# Übung zu Betriebssysteme

**Interruptb**ehandlung

14. November 2024

Maximilian Ott, Dustin Nguyen, Phillip Raffeck & Bernhard Heinloth

Lehrstuhl für Informatik 4 Friedrich-Alexander-Universität Erlangen-Nürnberg

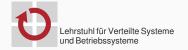

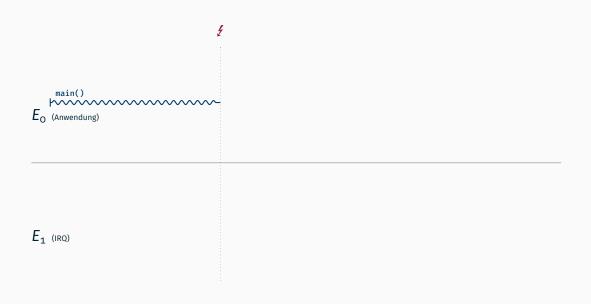

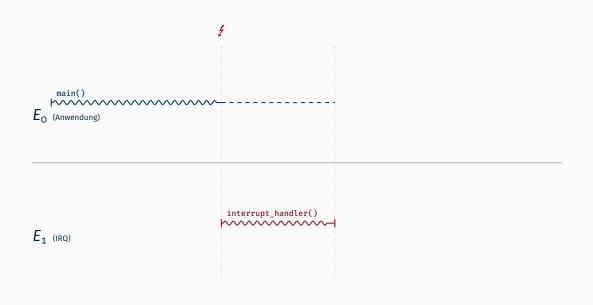

**Interrupts und Traps**

CPU

$$E_{\text{O}} \text{ (Anwendung)}$$

$E_1$  (IRQ)

Minimaler zu sichernder Zustand?

### Minimaler zu sichernder Zustand?

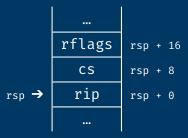

■ CPU sichert automatisch

rip Instruktionszeiger/Rücksprungadresserflags Status/Condition Codescs Aktuelles Code Segment

### Minimaler zu sichernder Zustand?

CPU sichert automatisch

rip Instruktionszeiger/Rücksprungadresserflags Status/Condition Codescs Aktuelles Code Segment

Wiederherstellung des ursprünglichen Prozessorzustandes durch Befehl iretq

```

;; Assembler

interrupt_entry:

;; Behandle IRQ

iretq

```

```

;; Assembler

interrupt_entry:

;; Behandle IRQ

;; in Hochsprache

call interrupt_handler

iretq

```

```

;; Assembler

interrupt_entry:

;; Behandle IRQ

;; in Hochsprache

call interrupt_handler

iretq

```

```

// C++

void interrupt_handler()

{

// Magie.

}

```

```

;; Assembler

interrupt_entry:

;; Behandle IRQ

;; in Hochsprache

call interrupt_handler

iretq

```

```

// C++

void interrupt_handler()

{

// Magie.

}

```

```

heinloth:~/oostubs$ make

LD .build/system64

build/interrupt/handler.asm.o: in function `interrupt_entry':

interrupt/handler.asm:(.text+0x16): undefined reference to `

interrupt_handler'

```

```

;; Assembler

interrupt_entry:

;; Behandle IRQ

;; in Hochsprache

call interrupt_handler

iretq

```

```

// C++

void interrupt_handler()

{

// Magie.

}

```

```

;; Assembler

interrupt_entry:

;; Behandle IRQ

;; in Hochsprache

call interrupt_handler

iretq

```

```

// C++ (mit C Linkage)

extern "C"

void interrupt_handler()

{

// Magie.

}

```

```

;; Assembler

interrupt_entry:

;; Behandle IRQ

;; in Hochsprache

call interrupt_handler

iretq

```

```

// C++ (mit C Linkage)

extern "C"

void interrupt_handler()

{

// Magie.

}

```

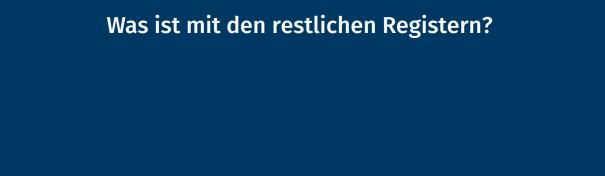

- Müssen durch den Interrupthandler selbst gesichert werden.

- entweder im Assembler-Teil oder

- der Compiler generiert bereits entsprechend Code

- Müssen durch den Interrupthandler selbst gesichert werden.

- entweder im Assembler-Teil oder

- der Compiler generiert bereits entsprechend Code

- Kontextsicherung beim Aufruf von Funktionen

- Müssen durch den Interrupthandler selbst gesichert werden.

- entweder im Assembler-Teil oder

- der Compiler generiert bereits entsprechend Code

- Kontextsicherung beim Aufruf von Funktionen

- 1. Aufrufende Funktion sichert alle Register, die sie braucht

- Müssen durch den Interrupthandler selbst gesichert werden.

- entweder im Assembler-Teil oder

- der Compiler generiert bereits entsprechend Code

- Kontextsicherung beim Aufruf von Funktionen

- 1. Aufrufende Funktion sichert alle Register, die sie braucht

- 2. Aufgerufene Funktion sichert alle Register, die sie verändert

- Müssen durch den Interrupthandler selbst gesichert werden.

- entweder im Assembler-Teil oder

- der Compiler generiert bereits entsprechend Code

- Kontextsicherung beim Aufruf von Funktionen

- 1. Aufrufende Funktion sichert alle Register, die sie braucht

- 2. <u>Aufgerufene</u> Funktion sichert alle Register, die sie verändert

- 3. Ein Teil der Register wird vom Aufrufer, ein anderer Teil vom Aufgerufenen gesichert

- Müssen durch den Interrupthandler selbst gesichert werden.

- entweder im Assembler-Teil oder

- der Compiler generiert bereits entsprechend Code

- Kontextsicherung beim Aufruf von Funktionen

- 1. Aufrufende Funktion sichert alle Register, die sie braucht

- 2. Aufgerufene Funktion sichert alle Register, die sie verändert

- 3. Ein Teil der Register wird vom Aufrufer, ein anderer Teil vom Aufgerufenen gesichert

- In der Praxis wird Variante 3 verwendet

- Aufteilung ist grundsätzlich compilerspezifisch

- Um Interoperabilität auf Binärcodeebene sicher zu stellen gibt es jedoch Konventionen (bei x64 zwei: Microsoft und System V)

- → Aufrufkonvention ist Teil der Application Binary Interface (ABI)

# Aufteilung der Register in zwei Gruppen

- Flüchtige Register (scratch registers, caller-save)

- Compiler geht davon aus, dass Unterprogramm den Inhalt verändert

- Aufrufer muss Inhalt gegebenenfalls sichern

- Beim x64 (nach System V ABI) sind rax, rcx, rdx, rsi, rdi und r8-r11 als flüchtig definiert

# Aufteilung der Register in zwei Gruppen

- Flüchtige Register (scratch registers, caller-save)

- Compiler geht davon aus, dass Unterprogramm den Inhalt verändert

- Aufrufer muss Inhalt gegebenenfalls sichern

- Beim x64 (nach System V ABI) sind rax, rcx, rdx, rsi, rdi und r8-r11 als flüchtig definiert

- Nicht-flüchtige Register (non-scratch registers, callee-save)

- Compiler geht davon aus, dass der Inhalt durch Unterprogramm nicht verändert wird

- Aufgerufene Funktion muss Inhalt gegebenenfalls sichern

- Beim x64 sind alle sonstigen Register als nicht-flüchtig definiert: rbx, rbp,

rsp und r12 r15

# Aufteilung der Register in zwei Gruppen

- Flüchtige Register (scratch registers, caller-save)

- Compiler geht davon aus, dass Unterprogramm den Inhalt verändert

- Aufrufer muss Inhalt gegebenenfalls sichern

- Beim x64 (nach System V ABI) sind rax, rcx, rdx, rsi, rdi und r8 r11 als flüchtig definiert

- Nicht-flüchtige Register (non-scratch registers, callee-save)

- Compiler geht davon aus, dass der Inhalt durch Unterprogramm nicht verändert wird

- Aufgerufene Funktion muss Inhalt gegebenenfalls sichern

- Beim x64 sind alle sonstigen Register als nicht-flüchtig definiert: rbx, rbp,

rsp und r12 r15

Unterbrechungsbehandlungen müssen auch flüchtige Register

# Unterbrechungsbehandlung (Kontextsicherung)

```

;; Assembler

interrupt_entry:

```

```

call interrupt_handler

```

iretq

# Unterbrechungsbehandlung (Kontextsicherung)

```

;; Assembler

interrupt_entry:

;; Kontext sichern

push rax

push rcx

;; ...

push r11

call interrupt_handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

# Unterbrechungsbehandlung (Kontext)

```

;; Assembler

// C++

interrupt_entry:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

call interrupt_handler

:: wiederherstellen

pop r11

extern "C"

void interrupt handler()

;; ...

pop rcx

// Magie.

pop rax

iretq

```

# Unterbrechungsbehandlung (Kontext)

```

;; Assembler

// C++

interrupt_entry:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

struct Context {

} attribute ((packed));

extern "C"

void interrupt handler(Context* c)

// Magie.

```

# Unterbrechungsbehandlung (Kontext)

```

;; Assembler

interrupt_entry:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

struct Context {

uint64 t r11;

// ...

uint64_t rcx;

uint64 t rax;

} attribute ((packed));

extern "C"

void interrupt handler(Context* c)

// Magie.

```

Parameterübergabe

# **Parameterübergabe**

- auf Stack

- bei x86 war dies gemäß der C declaration der Standard

## **Parameterübergabe**

- auf Stack

- bei x86 war dies gemäß der C declaration der Standard

- in Register

- Vorteil: schneller

- Problem: Anzahl der Register begrenzt

- kombiniert

- die ersten Parameter via Register, danach bei Bedarf Stack

## **Parameterübergabe**

- auf Stack

- bei x86 war dies gemäß der C declaration der Standard

- in Register

- Vorteil: schneller

- Problem: Anzahl der Register begrenzt

- kombiniert

- die ersten Parameter via Register, danach bei Bedarf Stack

- auch nach x64 System V ABI:

- Parameter zuerst in Register rdi, rsi, rdx, rcx, r8 und r9

- im Userspace danach auch in die Register xmm0 xmm7

- Rest auf Stack (letzter Parameter wird als erstes gepushed)

## Unterbrechungsbehandlung (Kontext)

```

;; Assembler

interrupt_entry:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

struct Context {

uint64 t r11;

// ...

uint64_t rcx;

uint64 t rax;

} attribute ((packed));

extern "C"

void interrupt handler(Context* c)

// Magie.

```

## **Unterbrechungsbehandlung (Kontext)**

```

;; Assembler

interrupt_entry:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

:: Pointer auf Stack

mov rdi, rsp

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

struct Context {

uint64 t r11;

// ...

uint64_t rcx;

uint64 t rax;

} attribute ((packed));

extern "C"

void interrupt handler(Context* c)

// Magie.

```

## **Unterbrechungsbehandlung (Kontext)**

```

;; Assembler

interrupt_entry:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

:: Pointer auf Stack

mov rdi, rsp

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

struct Context {

uint64 t r11;

// ...

uint64_t rcx;

uint64 t rax;

uint64 t rip;

uint64_t cs;

uint64 t rflags;

} attribute ((packed));

extern "C"

void interrupt handler(Context* c)

// Magie.

```

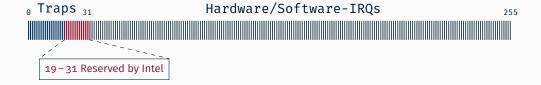

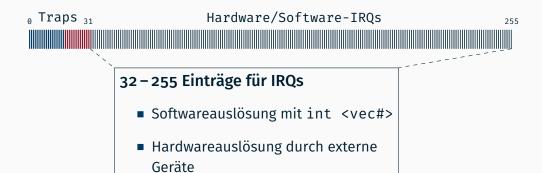

Hardware/Software-IRQs

<sub>0</sub> Traps <sub>31</sub> Division-by-Zero 0 **Debug Exception** Non-Maskable Interrupt(NMI) Breakpoint (INT 3) Overflow Exception **Bound Exception** Invalid Opcode FPU not Available Double Fault Invalid TSS Segment not Present Stack Exception General Protection Fault 13 Page Fault 14 Floating-Point Error Alignment Check Machine Check

255

<sub>0</sub> Traps <sub>31</sub> Division-by-Zero 0 **Debug Exception** Non-Maskable Interrupt(NMI) Breakpoint (INT 3) Overflow Exception **Bound Exception Invalid Opcode** FPU not Available Double Fault Invalid TSS Segment not Present Stack Exception **General Protection Fault** 13 Page Fault 14 Floating-Point Error Alignment Check Machine Check

Hardware/Software-IRQs

255

Hardware/Software-IRQs

<sub>0</sub> Traps <sub>31</sub> Division-by-Zero 0 **Debug Exception** Non-Maskable Interrupt(NMI) Breakpoint (INT 3) Overflow Exception **Bound Exception** Invalid Opcode FPU not Available Double Fault Invalid TSS Segment not Present Stack Exception General Protection Fault 13 Page Fault 14 Floating-Point Error Alignment Check Machine Check

255

Kann durch Prozessorbefehle maskiert werden

cli (clear interrupt flag) Interruptleitung sperren

sti (set interrupt flag) Interruptleitung freigeben

```

;; Assembler

interrupt_entry:

;; Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

call interrupt handler

;; wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

extern "C"

void interrupt handler(

Context* c

// Magie:

```

```

;; Assembler

interrupt_entry:

;; Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

extern "C"

void interrupt handler(

Context* c

// Magie:

switch (

){

case KBD:

kbd.magic();

break;

case TMR:

tmr.magic();

break;

```

```

;; Assembler

interrupt_entry:

;; Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

extern "C"

void interrupt handler(

Context* c

// Magie:

switch (vector){

case KBD:

kbd.magic();

break;

case TMR:

tmr.magic();

break;

```

```

;; Assembler

interrupt_entry:

;; Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

extern "C"

void interrupt handler(

Context* c,

uint32_t vector

// Magie:

switch (vector){

case KBD:

kbd.magic();

break;

case TMR:

tmr.magic();

break;

```

## Unterbrechungsbehandlung (für Vektor 6)

```

;; Assembler

interrupt_entry_6:

;; Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

call interrupt_handler

;; wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

extern "C"

void interrupt handler(

Context* c,

uint32_t vector

// Magie:

switch (vector){

case KBD:

kbd.magic();

break;

case TMR:

tmr.magic();

break;

```

## Unterbrechungsbehandlung (für Vektor 6)

```

:: Assembler

interrupt_entry_6:

;; Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

;; Vektornummer

mov rsi, 6

call interrupt_handler

;; wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

// C++

extern "C"

void interrupt handler(

Context* c,

uint32_t vector

// Magie:

switch (vector){

case KBD:

kbd.magic();

break;

case TMR:

tmr.magic();

break;

```

#### Unterbrechungsbehandlung (für Vektor 6)

```

:: Assembler

interrupt entry 6:

;; Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

;; Vektornummer

mov rsi, 6

call interrupt handler

:: wiederherstellen

pop r11

;; ...

pop rcx

pop rax

iretq

```

```

heinloth:~/oostubs$ make

ASM interrupt/handler.asm

CXX interrupt/handler.cc

LD .build/system64

```

```

:: Assembler

interrupt entry 6:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

;; Vektornummer

mov rsi, 6

call interrupt handler

:: wiederherstellen

pop r11

:: ...

pop rcx

pop rax

iretq

```

```

heinloth:~/oostubs$ make

ASM interrupt/handler.asm

CXX interrupt/handler.cc

LD .build/system64

```

```

10070f0 <interrupt_handler>

```

```

:: Assembler

interrupt entry 6:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

;; Vektornummer

mov rsi, 6

call 0x10070f0 <interrupt handler>

:: wiederherstellen

pop r11

:: ...

pop rcx

pop rax

iretq

```

```

heinloth:~/oostubs$ make

ASM interrupt/handler.asm

CXX interrupt/handler.cc

build/system64

```

```

10070f0 <interrupt_handler>

```

```

Maschinencode

50

51

41 53

48 89 e7

be 06 00 00 00

e8 a6 6e 00 00

41 5b

59

58

48 cf

```

```

on heinloth:~/oostubs$ make

on ASM interrupt/handler.asm

on CXX interrupt/handler.cc

on LD .build/system64

```

```

10070f0 <interrupt_handler>

```

| Speicher<br>adresse  | Maschinencode  |

|----------------------|----------------|

| 1000230:<br>1000231: | 50<br>51       |

| 1000231:             | 41 53          |

| 100023d:             | 48 89 e7       |

| 1000234.             | be 06 00 00 00 |

| 1000245:             | e8 a6 6e 00 00 |

| 100024a:             | 41 5b          |

| 1000255:<br>1000256: | 59<br>58       |

| 1000257:             | 48 cf          |

```

on heinloth:~/oostubs$ make

on ASM interrupt/handler.asm

on CXX interrupt/handler.cc

on LD .build/system64

```

```

100 70f0 <interrupt_handler>

```

| Speicher<br>adresse  | Maschinencode  |

|----------------------|----------------|

| 1000230:<br>1000231: | 50<br>51       |

| 100023b:             | 41 53          |

| 100023d:             | 48 89 e7       |

| 1000240:             | be 06 00 00 00 |

| 1000245:             | e8 a6 6e 00 00 |

| 100024a:             | 41 5b          |

| 1000255:             | 59             |

| 1000256:             | 58             |

| 1000257:             | 48 cf          |

```

heinloth:~/oostubs$ make

ASM interrupt/handler.asm

CXX interrupt/handler.cc

LD .build/system64

Speicheradressen beim Binden:

100 70f0 <interrupt_handler>

```

100 0230 <interrupt entry 6>

```

:: Assembler

interrupt entry 6:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

;; Vektornummer

mov rsi, 6

call interrupt handler

:: wiederherstellen

pop r11

:: ...

pop rcx

pop rax

iretq

```

```

heinloth:~/oostubs$ make

ASM interrupt/handler.asm

CXX interrupt/handler.cc

LD .build/system64

```

Speicheradressen beim Binden:

```

10070f0 <interrupt_handler>

```

100 0230 <interrupt\_entry\_6>

```

%macro IRQ 1

align 8

interrupt entry %1:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

;; Pointer auf Stack

mov rdi, rsp

;; Vektornummer

mov rsi, %1

call interrupt handler

:: wiederherstellen

pop r11

:: ...

pop rcx

pop rax

iretq

%endmacro

```

```

heinloth:~/oostubs$ make

ASM interrupt/handler.asm

CXX interrupt/handler.cc

LD .build/system64

```

Speicheradressen beim Binden:

```

10070f0 <interrupt_handler>

```

100 0230 <interrupt\_entry\_6>

```

%macro IRQ 1

align 8

interrupt entry %1:

:: Kontext sichern

push rax

push rcx

;; ...

push r11

:: Pointer auf Stack

mov rdi, rsp

;; Vektornummer

mov rsi, %1

call interrupt handler

:: wiederherstellen

pop r11

:: ...

pop rcx

pop rax

ireta

%endmacro

```

```

heinloth:~/oostubs$ make

ASM interrupt/handler.asm

CXX interrupt/handler.cc

LD .build/system64

```

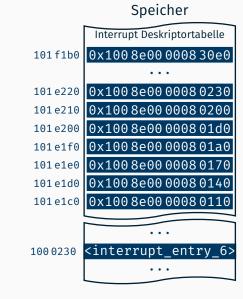

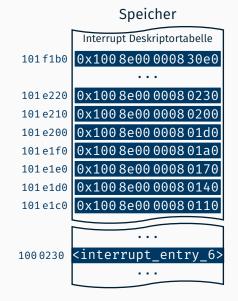

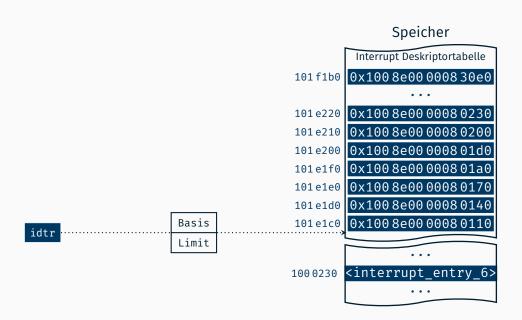

```

100 70f0 <interrupt_handler>

...

100 0230 <interrupt_entry_6>

100 0200 <interrupt_entry_5>

100 01d0 <interrupt_entry_4>

100 01a0 <interrupt_entry_3>

100 0170 <interrupt_entry_2>

100 0140 <interrupt_entry_1>

100 0110 <interrupt_entry_0>

```

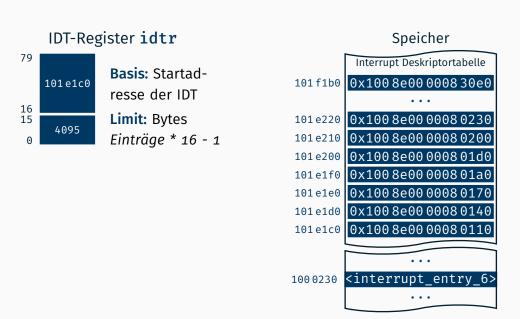

Woher weiß die CPU wo die entsprechende

**Unterbrechungsbehandlung liegt?**

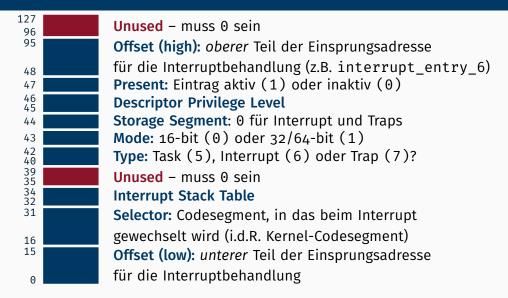

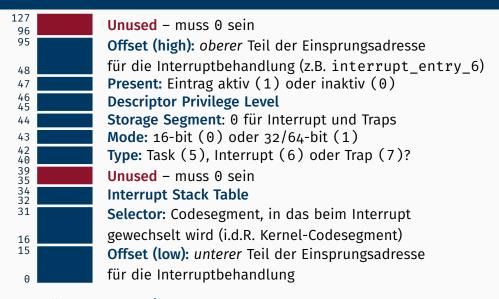

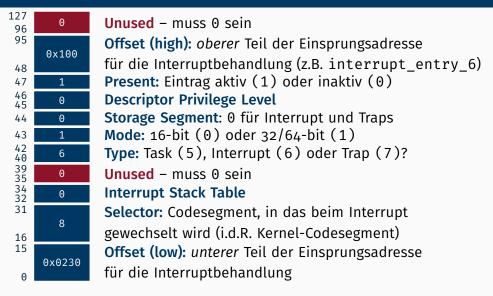

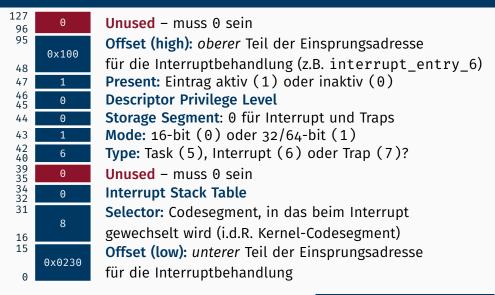

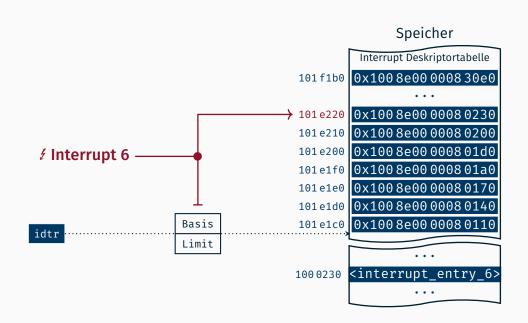

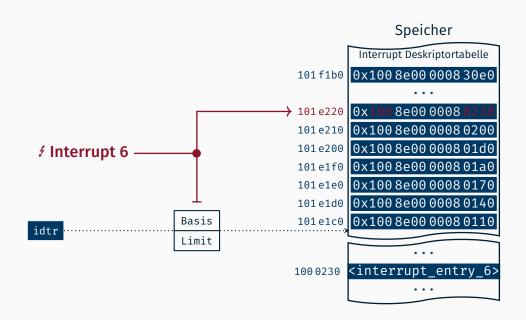

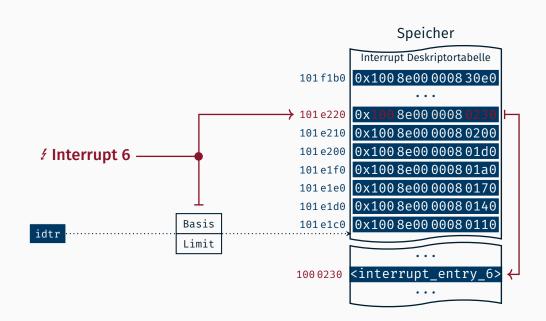

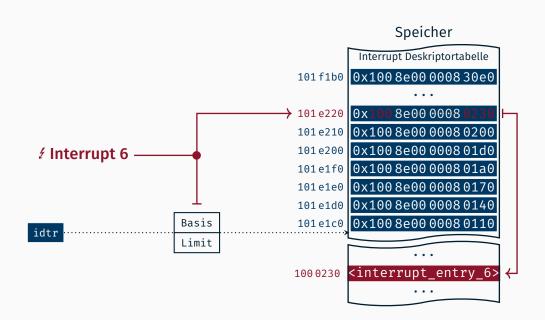

#### **Interrupt Deskriptor**

## Interrupt Deskriptor (Beispiel)

für 100 0230 <interrupt\_entry\_6>

## Interrupt Deskriptor (Beispiel)

für 100 0230 <interrupt\_entry\_6>

#### Interrupt Deskriptor (Beispiel)

für 100 0230 <interrupt\_entry\_6> → 0x100 8e00 0008 0230

```

► 0x1008e00000830e0

100 30e0 <interrupt entry 255>-

100 0230 <interrupt entry 6>—

► 0x1008e0000080230

100 0200 <interrupt_entry_5>—

► 0x1008e0000080200

100 01d0 <interrupt entry 4>----

► 0x1008e00000801d0

100 01a0 <interrupt entry 3>----

→ 0x100 8e00 0008 01a0

100 0170 <interrupt_entry_2>----

► 0x1008e0000080170

100 0140 <interrupt entry 1>-

► 0x1008e0000080140

100 0110 <interrupt entry 0>----

► 0x1008e0000080110

```

```

100 30e0 <interrupt_entry_255>

...

100 0230 <interrupt_entry_6>

100 0200 <interrupt_entry_5>

100 01d0 <interrupt_entry_4>

100 01a0 <interrupt_entry_3>

100 0170 <interrupt_entry_2>

100 0140 <interrupt_entry_1>

100 0110 <interrupt_entry_0>

```

#### Speicher

```

Interrupt Deskriptortabelle

0x1008e00000830e0

0x1008e0000080230

0x1008e0000080200

0x1008e00000801d0

0x1008e00000801a0

0x1008e0000080170

0x1008e0000080140

0x1008e0000080110

```

# 100 30e0 <interrupt\_entry\_255> ... 100 0230 <interrupt\_entry\_6> 100 0200 <interrupt\_entry\_5> 100 01d0 <interrupt\_entry\_4> 100 01a0 <interrupt\_entry\_3> 100 0170 <interrupt\_entry\_2> 100 0140 <interrupt\_entry\_1> 100 0110 <interrupt\_entry\_0>

#### Speicher

Interrupt Deskriptortabelle 101 f1b0 0x100 8e00 0008 30e0 101 e220 0x100 8e00 0008 0230 101 e210 0x100 8e00 0008 0200 101 e200 0x100 8e00 0008 01d0 101 e1f0 0x100 8e00 0008 01a0 101 e1e0 | 0x100 8e00 0008 0170 101 e1d0 | 0x100 8e00 0008 0140 101e1c0 0x1008e0000080110

# Speicher Interrupt Deskriptortabelle 101 f1b0 0x100 8e00 0008 30e0 101 e220 0x100 8e00 0008 0230 101 e210 0x100 8e00 0008 0200 101 e200 0x100 8e00 0008 01d0 101e1f0 0x1008e00000801a0 101 e1e0 0x100 8e00 0008 0170 101 e1d0 | 0x100 8e00 0008 0140 101 e1c0 0x100 8e00 0008 0110 <interrupt\_entry\_6> 100 0230 . . .

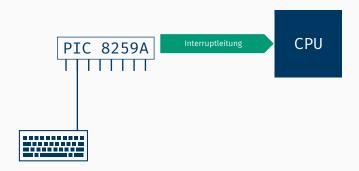

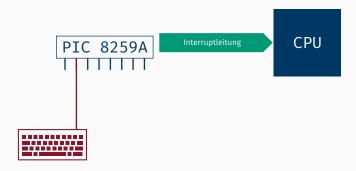

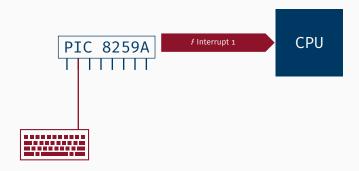

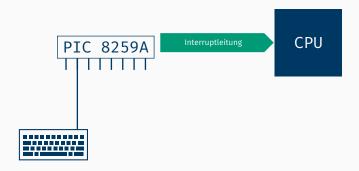

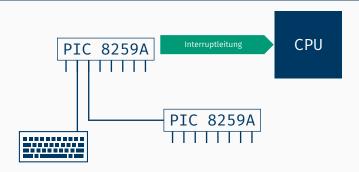

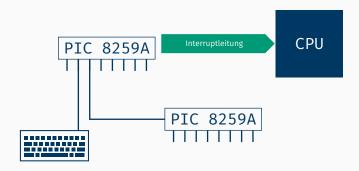

# Externe Interrupts

Anschluss von mehreren Geräten durch Programmable Interrupt Controller

- Anschluss von mehreren Geräten durch Programmable Interrupt Controller

- feste Prioritätenreihenfolge

- Interruptvektornummer bedingt änderbar (Vielfaches von 8)

- Konfiguration über I/O-Ports

- Anschluss von mehreren Geräten durch Programmable Interrupt Controller

- feste Prioritätenreihenfolge

- Interruptvektornummer bedingt änderbar (Vielfaches von 8)

- Konfiguration über I/O-Ports

- Anschluss von mehreren Geräten durch Programmable Interrupt Controller

- feste Prioritätenreihenfolge

- Interruptvektornummer bedingt änderbar (Vielfaches von 8)

- Konfiguration über I/O-Ports

- Anschluss von mehreren Geräten durch Programmable Interrupt Controller

- feste Prioritätenreihenfolge

- Interruptvektornummer bedingt änderbar (Vielfaches von 8)

- Konfiguration über I/O-Ports

- Anschluss von mehreren Geräten durch Programmable Interrupt Controller

- feste Prioritätenreihenfolge

- Interruptvektornummer bedingt änderbar (Vielfaches von 8)

- Konfiguration über I/O-Ports

- Anschluss von mehreren Geräten durch Programmable Interrupt Controller

- feste Prioritätenreihenfolge

- Interruptvektornummer bedingt änderbar (Vielfaches von 8)

- Konfiguration über I/O-Ports

- Erweiterung von 8 auf 15 Geräte durch Kaskadierung

- Anschluss von mehreren Geräten durch Programmable Interrupt Controller

- feste Prioritätenreihenfolge

- Interruptvektornummer bedingt änderbar (Vielfaches von 8)

- Konfiguration über I/O-Ports

- Erweiterung von 8 auf 15 Geräte durch Kaskadierung

- Nicht für Mehrprozessorsysteme geeignet

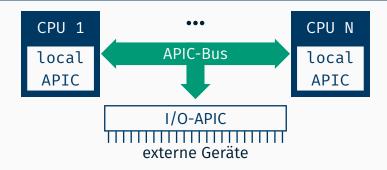

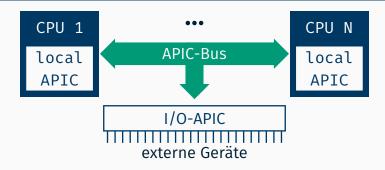

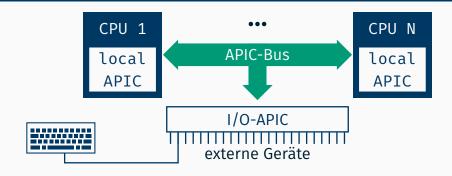

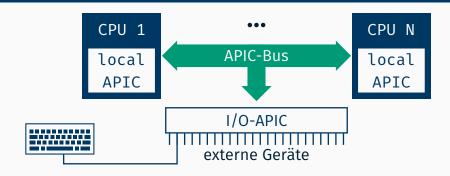

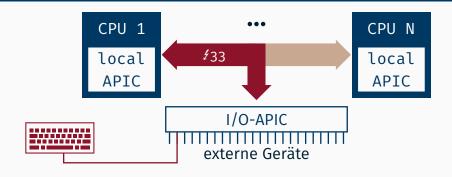

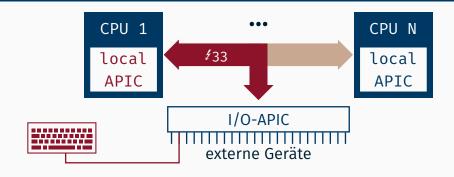

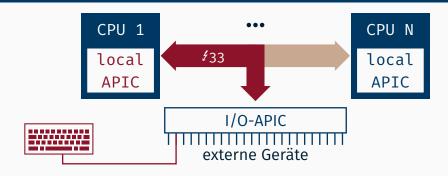

**Externe Interrupts mit dem APIC**

Aufteilung in lokalen APIC und I/O APIC

- Zuweisung von beliebigen Vektornummern

- Aktivieren und Deaktivieren von einzelnen Interruptquellen

- Zuweisung von Zielprozessoren für einzelnen Interrupt in MP-Systemen

- Zuweisung von beliebigen Vektornummern

- Aktivieren und Deaktivieren von einzelnen Interruptquellen

- Zuweisung von Zielprozessoren für einzelnen Interrupt in MP-Systemen

- Zuweisung von beliebigen Vektornummern

- Aktivieren und Deaktivieren von einzelnen Interruptquellen

- Zuweisung von Zielprozessoren für einzelnen Interrupt in MP-Systemen

Interrupts werden zu Nachrichten auf dem APIC-Bus

Empfang durch Local APIC

#### **Empfang durch Local APIC**

- Verbindet eine CPU mit dem APIC-Bus

- Liest Nachrichten vom APIC-Bus und unterbricht die CPU

- Muss Interrupts explizit quittieren (ACK)

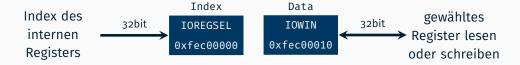

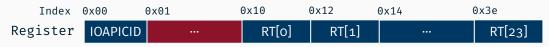

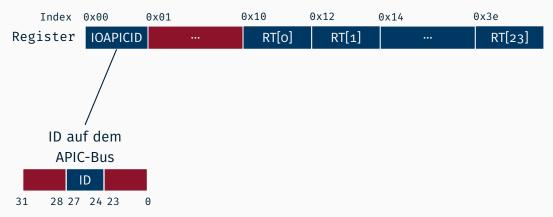

# Programmierung des Intel I/O-APIC

Zugriff auf die internen Register über memory-mapped I/O

# Programmierung des Intel I/O-APIC

Zugriff auf die internen Register über memory-mapped I/O

Jedoch keine direkte Abbildung von internen Registern auf Speicheradressen

## Programmierung des Intel I/O-APIC

#### Zugriff auf die internen Register über memory-mapped I/O

- Jedoch keine direkte Abbildung von internen Registern auf Speicheradressen

- Umweg über ein Index- und Datenregister

## Programmierung des Intel I/O-APIC

#### Zugriff auf die internen Register über memory-mapped I/O

- Jedoch keine direkte Abbildung von internen Registern auf Speicheradressen

- Umweg über ein Index- und Datenregister

## Programmierung des Intel I/O-APIC

#### Zugriff auf die internen Register über memory-mapped I/O

- Jedoch keine direkte Abbildung von internen Registern auf Speicheradressen

- Umweg über ein Index- und Datenregister

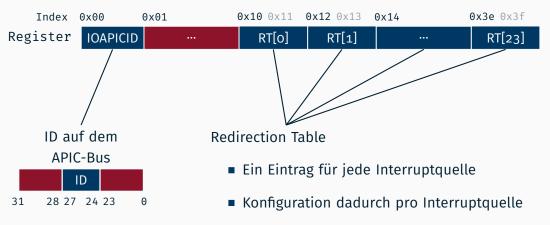

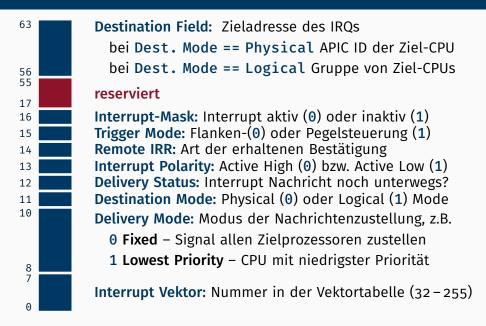

## Programmierung des Intel I/O-APIC (2)

#### Interne Register des I/O-APICs

## Programmierung des Intel I/O-APIC (2)

#### Interne Register des I/O-APICs

## Programmierung des Intel I/O-APIC (2)

#### Interne Register des I/O-APICs

Zwei interne Register pro Eintrag (64bit)

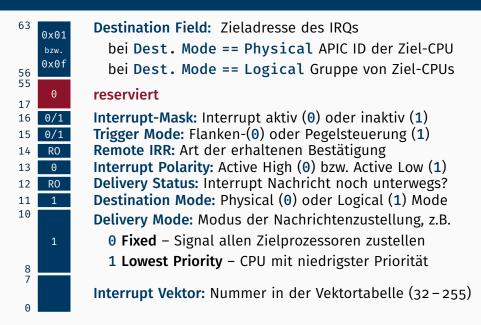

#### **Aufbau eines Redirection Table Eintrags**

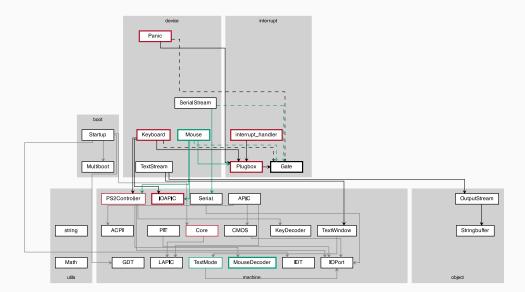

# Umsetzung in StuBS

#### Wo ist welches Gerät angeschlossen?

■ Das kann evtl. unterschiedlich sein von Rechner zu Rechner!

- Das kann evtl. unterschiedlich sein von Rechner zu Rechner!

- Steht in der Systemkonfiguration, heutzutage i.d.R. ACPI (Advanced Configuration and Power Interface)

- Das kann evtl. unterschiedlich sein von Rechner zu Rechner!

- Steht in der Systemkonfiguration, heutzutage i.d.R. ACPI (Advanced Configuration and Power Interface)

- Bei uns stellt APIC die relevanten Teile dieser Informationen bereit

- Das kann evtl. unterschiedlich sein von Rechner zu Rechner!

- Steht in der Systemkonfiguration, heutzutage i.d.R. ACPI (Advanced Configuration and Power Interface)

- Bei uns stellt APIC die relevanten Teile dieser Informationen bereit APIC::getIOAPICSlot liefert für jedes Gerät den Index in die Redirection Table (siehe enum Device in machine/apic.h)

#### Wo ist welches Gerät angeschlossen?

- Das kann evtl. unterschiedlich sein von Rechner zu Rechner!

- Steht in der Systemkonfiguration, heutzutage i.d.R. ACPI (Advanced Configuration and Power Interface)

- Bei uns stellt APIC die relevanten Teile dieser Informationen bereit APIC::getIOAPICSlot liefert für jedes Gerät den Index in die Redirection Table (siehe enum Device in machine/apic.h)

APIC::getIOAPICID liefert die ID des I/O-APICs

- Zusammenspiel mehrerer Faktoren

- Destination Mode, Destination Field und Delivery Mode im I/O-APIC

- Prozessor Priorität in den Local APICs der einzelnen CPUs

- Zusammenspiel mehrerer Faktoren

- Destination Mode, Destination Field und Delivery Mode im I/O-APIC

- Prozessor Priorität in den Local APICs der einzelnen CPUs

- **Ziel:** Gleichverteilung der Interrupts auf alle CPUs

- Zusammenspiel mehrerer Faktoren

- Destination Mode, Destination Field und Delivery Mode im I/O-APIC

- Prozessor Priorität in den Local APICs der einzelnen CPUs

- **Ziel:** Gleichverteilung der Interrupts auf alle CPUs

- Priorität der Prozessoren im Local APIC fest auf 0 einstellen

- Zusammenspiel mehrerer Faktoren

- Destination Mode, Destination Field und Delivery Mode im I/O-APIC

- Prozessor Priorität in den Local APICs der einzelnen CPUs

- **Ziel:** Gleichverteilung der Interrupts auf alle CPUs

- Priorität der Prozessoren im Local APIC fest auf 0 einstellen

- Im I/O-APIC Lowest Priority als Delivery Mode verwenden

- Zusammenspiel mehrerer Faktoren

- Destination Mode, Destination Field und Delivery Mode im I/O-APIC

- Prozessor Priorität in den Local APICs der einzelnen CPUs

- **Ziel:** Gleichverteilung der Interrupts auf alle CPUs

- Priorität der Prozessoren im Local APIC fest auf 0 einstellen

- Im I/O-APIC Lowest Priority als Delivery Mode verwenden

- Verwendung des Logical Destination Mode; bis zu 8 CPUs adressierbar

- Zusammenspiel mehrerer Faktoren

- Destination Mode, Destination Field und Delivery Mode im I/O-APIC

- Prozessor Priorität in den Local APICs der einzelnen CPUs

- **Ziel:** Gleichverteilung der Interrupts auf alle CPUs

- Priorität der Prozessoren im Local APIC fest auf 0 einstellen

- Im I/O-APIC Lowest Priority als Delivery Mode verwenden

- Verwendung des Logical Destination Mode; bis zu 8 CPUs adressierbar

- Destination Field: Bitmaske mit gesetztem Bit pro aktivierter CPU

## Redirection Table Einträge in StuBS

(RO: Read Only)

| Keyboard Interrupt in StuBS |  |

|-----------------------------|--|

|                             |  |

Zusammenfassendes Beispiel:

■ I/O APIC initialisieren

- I/O APIC initialisieren

- I/O APIC ID setzen

- I/O APIC initialisieren

- I/O APIC ID setzen

- Einträge in Redirection Table initialisieren (deaktivieren)

- I/O APIC initialisieren

- I/O APIC ID setzen

- Einträge in **Redirection Table** initialisieren (deaktivieren)

- **Keyboard** konfigurieren

- I/O APIC initialisieren

- I/O APIC ID setzen

- Einträge in Redirection Table initialisieren (deaktivieren)

- **Keyboard** konfigurieren

- Anmelden bei der Plugbox

- I/O APIC initialisieren

- I/O APIC ID setzen

- Einträge in Redirection Table initialisieren (deaktivieren)

- Keyboard konfigurieren

- Anmelden bei der Plugbox

- Tastaturslot herausfinden und den entsprechenden Eintrag in der Redirection Table konfigurieren und aktivieren

- Tastaturbuffer leeren

- I/O APIC initialisieren

- I/O APIC ID setzen

- Einträge in Redirection Table initialisieren (deaktivieren)

- **Keyboard** konfigurieren

- Anmelden bei der Plugbox

- Tastaturslot herausfinden und den entsprechenden Eintrag in der Redirection Table konfigurieren und aktivieren

- Tastaturbuffer leeren

- Interruptbehandlung erstellen

- Einsprungsroutinen interrupt\_entry mit Aufruf zu interrupt\_handler schreiben [wird in der Vorgabe bereits erledigt]

- I/O APIC initialisieren

- I/O APIC ID setzen

- Einträge in Redirection Table initialisieren (deaktivieren)

- Keyboard konfigurieren

- Anmelden bei der Plugbox

- Tastaturslot herausfinden und den entsprechenden Eintrag in der Redirection Table konfigurieren und aktivieren

- Tastaturbuffer leeren

- Interruptbehandlung erstellen

- Einsprungsroutinen interrupt\_entry mit Aufruf zu interrupt\_handler schreiben [wird in der Vorgabe bereits erledigt]

- Eintragen in die Interrupt Deskriptor Tabelle (IDT) und diese in das Register idtr laden [ebenfalls erledigt]

- I/O APIC initialisieren

- I/O APIC ID setzen

- Einträge in Redirection Table initialisieren (deaktivieren)

- Keyboard konfigurieren

- Anmelden bei der Plugbox

- Tastaturslot herausfinden und den entsprechenden Eintrag in der Redirection Table konfigurieren und aktivieren

- Tastaturbuffer leeren

- Interruptbehandlung erstellen

- Einsprungsroutinen interrupt\_entry mit Aufruf zu interrupt\_handler schreiben [wird in der Vorgabe bereits erledigt]

- Eintragen in die Interrupt Deskriptor Tabelle (IDT) und diese in das Register idtr laden [ebenfalls erledigt]

- Ereignisbehandlung in interrupt\_handler mittels Plugbox

- I/O APIC initialisieren

- I/O APIC ID setzen

- Einträge in Redirection Table initialisieren (deaktivieren)

- Keyboard konfigurieren

- Anmelden bei der Plugbox

- Tastaturslot herausfinden und den entsprechenden Eintrag in der Redirection Table konfigurieren und aktivieren

- Tastaturbuffer leeren

- Interruptbehandlung erstellen

- Einsprungsroutinen interrupt\_entry mit Aufruf zu interrupt\_handler schreiben [wird in der Vorgabe bereits erledigt]

- Eintragen in die Interrupt Deskriptor Tabelle (IDT) und diese in das Register idtr laden [ebenfalls erledigt]

- Ereignisbehandlung in interrupt\_handler mittels Plugbox

- Interrupts mit Core::Interrupt::enable() aktivieren

#### **Ablauf**

#### **Ablauf**

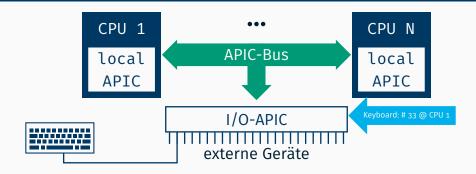

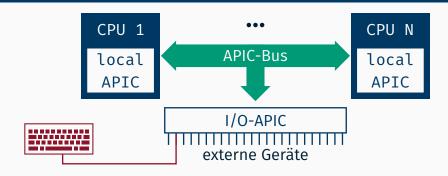

Tastendruck – Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. PS/2-Controller aktiviert Interruptleitung zu I/O APIC

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. **PS/2-Controller** aktiviert Interruptleitung zu **I/O APIC**

- 2.1 Anhand der Redirection Table wird Aktion gewählt

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. **PS/2-Controller** aktiviert Interruptleitung zu **I/O APIC**

- 2.1 Anhand der Redirection Table wird Aktion gewählt

- 2.2 Nachricht auf APIC-Bus mit Interruptnr. 33 und Ziel-CPU

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. **PS/2-Controller** aktiviert Interruptleitung zu **I/O APIC**

- 2.1 Anhand der Redirection Table wird Aktion gewählt

- 2.2 Nachricht auf APIC-Bus mit Interruptnr. 33 und Ziel-CPU

- 3. entsprechender LAPIC empfängt Nachricht vom APIC-Bus

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. **PS/2-Controller** aktiviert Interruptleitung zu **I/O APIC**

- 2.1 Anhand der Redirection Table wird Aktion gewählt

- 2.2 Nachricht auf APIC-Bus mit Interruptnr. 33 und Ziel-CPU

- entsprechender LAPIC empfängt Nachricht vom APIC-Bus und unterbricht CPU

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. PS/2-Controller aktiviert Interruptleitung zu I/O APIC

- 2.1 Anhand der Redirection Table wird Aktion gewählt

- 2.2 Nachricht auf APIC-Bus mit Interruptnr. 33 und Ziel-CPU

- entsprechender LAPIC empfängt Nachricht vom APIC-Bus und unterbricht CPU

- 4. CPU führt Unterbrechungsbehandlung aus

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. PS/2-Controller aktiviert Interruptleitung zu I/O APIC

- 2.1 Anhand der Redirection Table wird Aktion gewählt

- 2.2 Nachricht auf APIC-Bus mit Interruptnr. 33 und Ziel-CPU

- entsprechender LAPIC empfängt Nachricht vom APIC-Bus und unterbricht CPU

- 4. CPU führt Unterbrechungsbehandlung aus

- 4.1 Mittels Register idtr wird der entsprechende Eintrag in der Interrupt

Deskriptor Tabelle ausgewählt und in die Einsprungsroutine

gesprungen

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. **PS/2-Controller** aktiviert Interruptleitung zu **I/O APIC**

- 2.1 Anhand der Redirection Table wird Aktion gewählt

- 2.2 Nachricht auf APIC-Bus mit Interruptnr. 33 und Ziel-CPU

- 3. entsprechender **LAPIC** empfängt Nachricht vom **APIC-Bus** und unterbricht CPU

- 4. CPU führt Unterbrechungsbehandlung aus

- 4.1 Mittels Register idtr wird der entsprechende Eintrag in der Interrupt Deskriptor Tabelle ausgewählt und in die Einsprungsroutine gesprungen

- 4.2 Einsprungsroutine interrupt\_entry\_33 sichert Register und ruft

interrupt\_handler mit Parameter vector = 33 auf

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. **PS/2-Controller** aktiviert Interruptleitung zu **I/O APIC**

- 2.1 Anhand der **Redirection Table** wird Aktion gewählt

- 2.2 Nachricht auf APIC-Bus mit Interruptnr. 33 und Ziel-CPU

- entsprechender LAPIC empfängt Nachricht vom APIC-Bus und unterbricht CPU

- 4. CPU führt Unterbrechungsbehandlung aus

- 4.1 Mittels Register idtr wird der entsprechende Eintrag in der Interrupt Deskriptor Tabelle ausgewählt und in die Einsprungsroutine gesprungen

- 4.2 Einsprungsroutine interrupt\_entry\_33 sichert Register und ruft

interrupt\_handler mit Parameter vector = 33 auf

- 4.3 interrupt\_handler behandelt mittels Plugbox den Interrupt

- Tastendruck Tastaturprozessor (in der Tastatur) meldet dies seriell an den PS/2-Controller

- 2. **PS/2-Controller** aktiviert Interruptleitung zu **I/O APIC**

- 2.1 Anhand der Redirection Table wird Aktion gewählt

- 2.2 Nachricht auf APIC-Bus mit Interruptnr. 33 und Ziel-CPU

- 3. entsprechender **LAPIC** empfängt Nachricht vom **APIC-Bus** und unterbricht CPU

- 4. CPU führt Unterbrechungsbehandlung aus

- 4.1 Mittels Register idtr wird der entsprechende Eintrag in der Interrupt Deskriptor Tabelle ausgewählt und in die Einsprungsroutine gesprungen

- 4.2 Einsprungsroutine interrupt\_entry\_33 sichert Register und ruft interrupt\_handler mit Parameter vector = 33 auf

- 4.3 interrupt\_handler behandelt mittels Plugbox den Interrupt

- 5. LAPIC quittiert die Behandlung

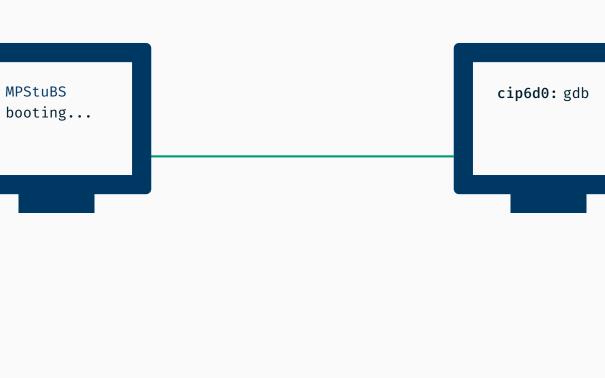

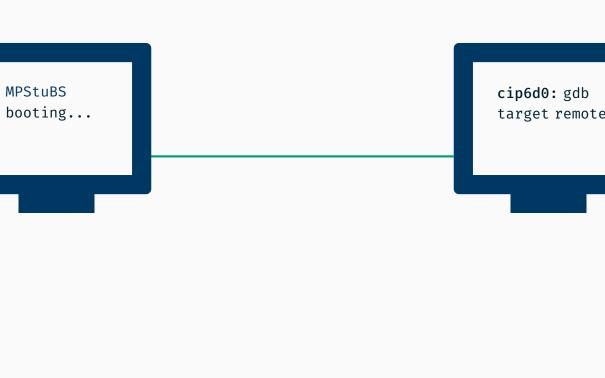

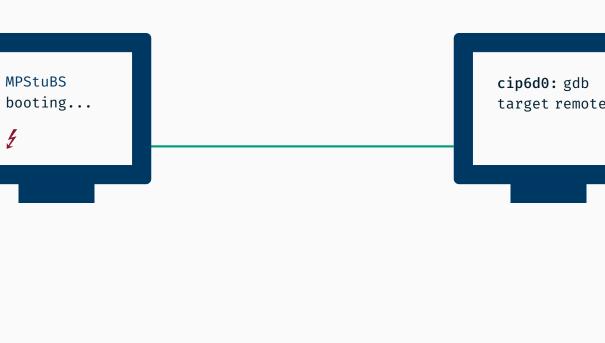

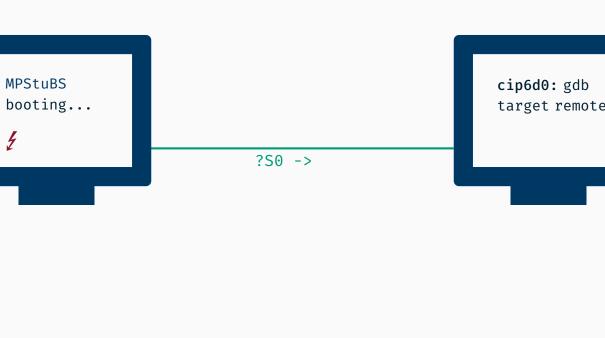

**Remotedebugging mit GDB**

# MPStuBS booting... cip6d0: gdb target remote invalid opcod (gdb)

Protokoll ist bereits implementiert

- Protokoll ist bereits implementiert

- verwendet eigene Unterbrechungsbehandlung für Traps

- Protokoll ist bereits implementiert

- verwendet eigene Unterbrechungsbehandlung für Traps

- → modifiziert die IDT

MPStuBS booting...

cip6d0: gdb

target remote

invalid opcod

(gdb)

- Protokoll ist bereits implementiert

- verwendet eigene Unterbrechungsbehandlung für Traps

- → modifiziert die IDT

- nur die serielle Schnittstelle (von Aufgabe 1) wird benötigt

MPStuBS booting...

cip6d0: gdb

(gdb)

target remote invalid opcod

- Protokoll ist bereits implementiert

- verwendet eigene Unterbrechungsbehandlung für Traps

- → modifiziert die IDT

- nur die serielle Schnittstelle (von Aufgabe 1) wird benötigt

- aber ist freiwillig

# Aufgabe 2

#### Lernziele

- Behandlung asynchroner Ereignisse

- Problematik und Schutz kritischer Abschnitte

### Lernziele

- Behandlung asynchroner Ereignisse

- Problematik und Schutz kritischer Abschnitte

## **Aufgabe**

- Konfiguration externer Geräte über I/O APIC

- Treiber für **Tastatur** und (*optional*) **Maus**

- Wechselseitiger Ausschluss (Ticket-/Spinlock)

- Optional: GDB Stub

■ Problem: Tastatur-Interrupts in KVM nur auf Core 1

- **Problem:** Tastatur-Interrupts in KVM nur auf Core 1

- Lösung: Datei /etc/modprobe.d/kvm\_options.conf editieren, Eintrag options kvm vector\_hashing=N hinzufügen und System neu starten.

# KVM nutzt ggf. Vector Hashing

- **Problem:** Tastatur-Interrupts in KVM nur auf Core 1

- Lösung: Datei /etc/modprobe.d/kvm\_options.conf editieren, Eintrag options kvm vector\_hashing=N hinzufügen und System neu starten.

(weitere Details siehe FAQ auf der Webseite)

# Fragen?

Abgabe der 2. Aufgabe bis Mittwoch, 27. November Nächste Woche ist wieder ein Seminar (21. November)