# WATWAOS: A Framework for <u>W</u>orst-Case-<u>A</u>ware <u>T</u>ailoring and <u>W</u>hole-System <u>A</u>nalysis of Energy-Constrained Real-Time Systems

December 3, 2025 46<sup>th</sup> IEEE Real-Time Systems Symposium, Boston, MA, USA

Tobias Häberlein, Eva Dengler, Phillip Raffeck, Peter Wägemann

Friedrich-Alexander-Universität Erlangen-Nürnberg Supported by the DFG under the grant WA 5186/1-1 (Watwa)

## **Embedded Real-Time Systems**

## **Embedded Real-Time Systems**

#### Requirements

- Safe worst-case timing and energy consumption bounds (WCET/WCEC)

- Energy-efficient operation

# **Energy-Constrained Real-Time Systems**

- Energy efficiency of embedded systems depends on

- The clock frequency

- The type of performed operation

## **Energy-Constrained Real-Time Systems**

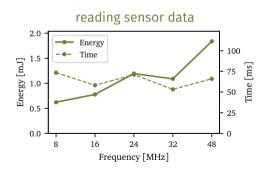

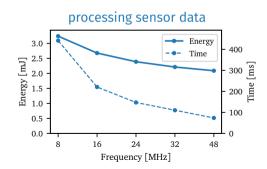

- Energy efficiency of embedded systems depends on

- The clock frequency

- The type of performed operation

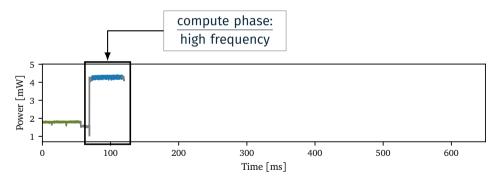

- lacktriangle Typical use case: read sensor data ightarrow process the obtained data

## **Energy-Constrained Real-Time Systems**

- Energy efficiency of embedded systems depends on

- The clock frequency

- The type of performed operation

- Typical use case: read sensor data → process the obtained data

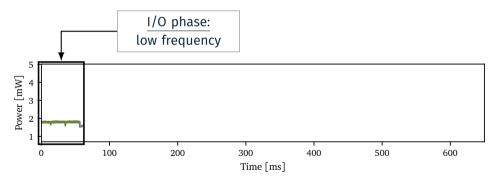

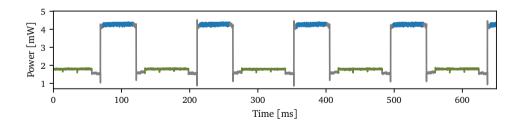

### **Dynamic Approaches**

■ Detect I/O and compute phases and change clock frequency accordingly

#### **Dynamic Approaches**

■ Detect I/O and compute phases and change clock frequency accordingly

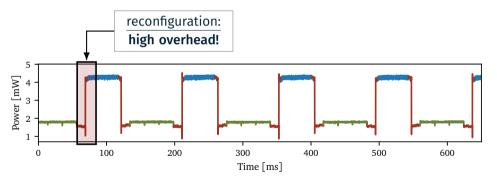

#### **Dynamic Approaches**

■ Detect I/O and compute phases and change clock frequency accordingly

#### **Dynamic Approaches**

■ Detect I/O and compute phases and change clock frequency accordingly

#### **Dynamic Approaches**

■ Detect I/O and compute phases and change clock frequency accordingly

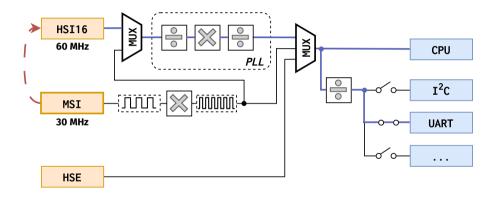

## **Clock Trees**

## **Clock Trees**

#### **Problem Statement**

How can we **save energy** to operate as long as possible, while still being able to give **real-time guarantees**?

#### **Problem Statement**

How can we **save energy** to operate as long as possible, while still being able to give **real-time guarantees**?

■ Minimize energy consumption while providing safe WCET/WCEC bounds

■ Keep analysis and optimization times reasonable

## Approach - Outline

How can we **save energy** to operate as long as possible, while still being able to give **real-time guarantees**?

#### In a Nutshell:

- Minimize energy consumption while providing safe WCET/WCEC bounds

- $\blacksquare \ \, \text{Construct global Power-State-Transition Graph}_{\, \texttt{[ECRTS'18]}} \to \text{perform IPET to get WCET/WCEC} \\$

- Keep analysis and optimization times reasonable

## **Approach - Outline**

How can we **save energy** to operate as long as possible, while still being able to give **real-time guarantees**?

#### In a Nutshell:

- Minimize energy consumption while providing safe WCET/WCEC bounds

- Construct global Power-State-Transition Graph [ECRTS '18] → perform IPET to get WCET/WCEC

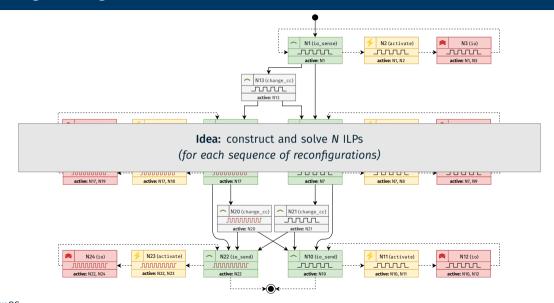

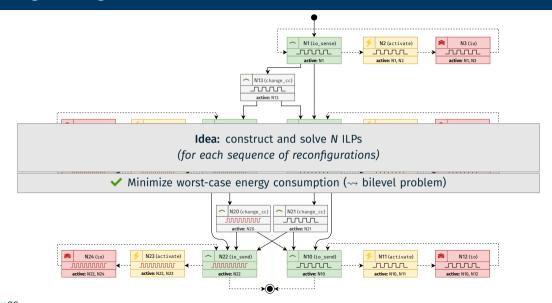

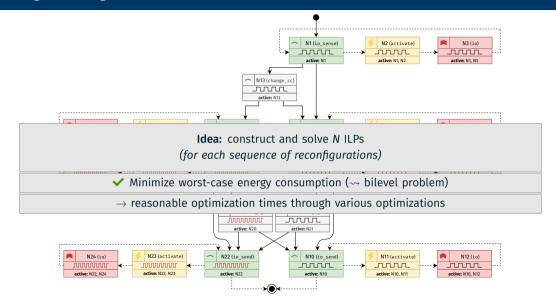

- lacksquare Introduce clock reconfiguration points ightarrow solve multiple ILPs

- Keep analysis and optimization times reasonable

## **Approach - Outline**

How can we **save energy** to operate as long as possible, while still being able to give **real-time guarantees**?

#### In a Nutshell:

- Minimize energy consumption while providing safe WCET/WCEC bounds

- $\hbox{ \bf Construct global Power-State-Transition Graph } _{\tt [ECRTS '18]} \rightarrow perform \ IPET \ to \ get \ WCET/WCEC \\$

- ullet Introduce clock reconfiguration points o solve multiple ILPs

- Keep analysis and optimization times reasonable

- Reduce ILP complexity with node merging techniques

- Make use of special solver features

## **System Model**

#### **Hardware**

- Resource-constrained system-on-chip platform

- Predictable architecture, no caches

- Complex clock-configuration networks

#### **Operating System**

- Fixed-priority, preemptive scheduler

- Statically known task set

- Independent tasks

- lacksquare Any number of sporadic task activations (ightarrow interrupts) allowed

#### Application:

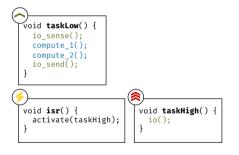

```

void taskLow() {

io_sense();

compute_1();

compute_2();

io_send();

}

void isr() {

activate(taskHigh);

}

void taskHigh() {

io();

}

```

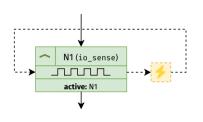

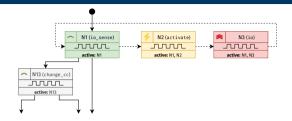

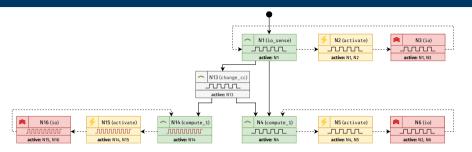

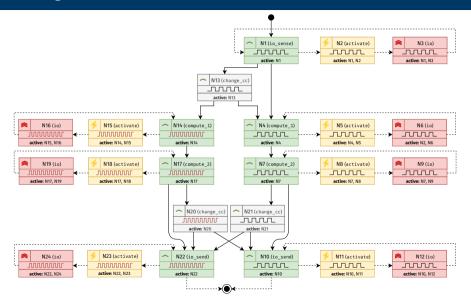

### Application:

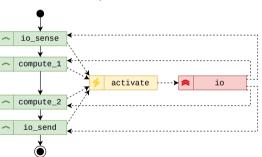

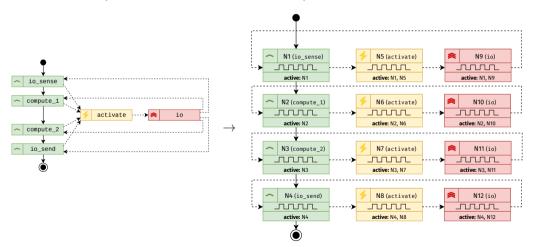

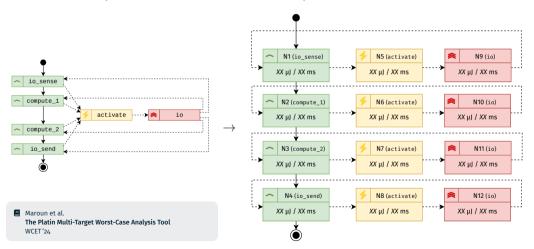

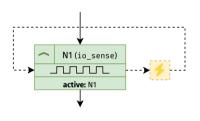

#### Control-Flow Graph:

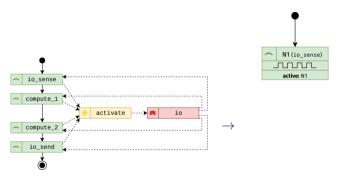

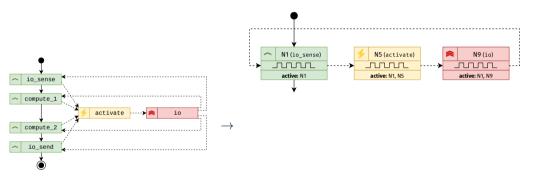

Control-Flow Graph  $\rightarrow$  Power-State-Transition Graph (PSTG):

Control-Flow Graph  $\rightarrow$  Power-State-Transition Graph (PSTG):

#### Control-Flow Graph $\rightarrow$ Power-State-Transition Graph (PSTG):

#### Control-Flow Graph $\rightarrow$ Power-State-Transition Graph (PSTG):

## ${\sf Control\text{-}Flow\;Graph} \to {\sf Power\text{-}State\text{-}Transition\;Graph} \ ({\sf PSTG}) \ \to {\sf ILP}$

## **Integer Linear Program**

#### **Constraints per node:**

- $\sum f(\text{Input Edge}) = \sum f(\text{Output Edge})$

- f(Node) =  $\sum f(Input Edges_{\neq ISR})$

**.**..

#### Other important constraints

- Loops: derive upper bound from source code

- ISRs: determine frequency using minimum inter-arrival time

## **Integer Linear Program**

#### **Constraints per node:**

- $\sum f(\text{Input Edge}) = \sum f(\text{Output Edge})$

- f(Node) =  $\sum f(Input Edges_{\neq ISR})$

- **.**..

#### Other important constraints

- Loops: derive upper bound from source code

- ISRs: determine frequency using minimum inter-arrival time

✓ Provide safe WCET/WCEC bounds

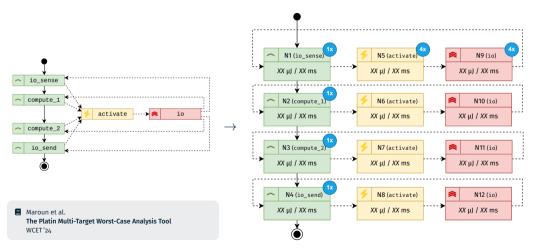

## **Adding Clock Reconfiguration Points**

```

void taskLow() {

io_sense();

compute_1();

compute_2();

io_send();

}

```

New: add clock reconfiguration nodes

- before/after single I/O operations

- before/after a loop with I/O operations

- at the start/end of a task

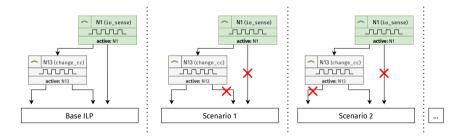

## Optimization: Exploiting Similarities in the Graph Construction

#### Optimization: Exploiting Similarities in the Graph Construction

- Idea: merge nodes and edges whenever possible

- Reduces the amount of constraints and variables in the ILP

- New constraints necessary to retain context-sensitive information

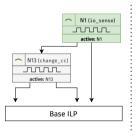

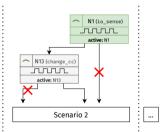

### Optimization: Exploiting Similarities in the ILP Formulation

- Previously: construct N ILPs

- Now: construct 1 base ILP with multiple scenarios

- Feature of the Gurobi solver

### Optimization: Exploiting Similarities in the ILP Formulation

- Previously: construct N ILPs

- Now: construct 1 base ILP with multiple scenarios

- Feature of the Gurobi solver

✓ Keep analysis and optimization times reasonable

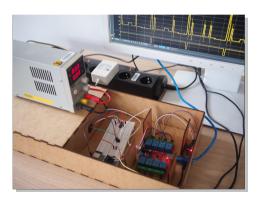

# Evaluation

#### Setup

**ESP32-C3**: 32-bit RISC-V CPU, max. 160  $\mathrm{MHz}$ , 400  $\mathrm{kB}$  SRAM

Energy measurement device: Joulescope JS220

## **Evaluation: Optimization Time (1)**

| Interrupts | Merging | Variables | Constraints | Solving time (first 3000 scenarios) |

|------------|---------|-----------|-------------|-------------------------------------|

| 0          | Off     | 98        | 87          | 0.10 s                              |

|            | On      | 98        | 87          | 0.10 s                              |

Watwa0S 15

## **Evaluation: Optimization Time (1)**

| Interrupts | Merging | Variables | Constraints | Solving time (first 3000 scenarios) |

|------------|---------|-----------|-------------|-------------------------------------|

| 0          | Off     | 98        | 87          | 0.10 s                              |

|            | On      | 98        | 87          | 0.10 s                              |

| 1          | Off     | 984       | 663         | 2.74s                               |

|            | On      | 270       | 238         | ■ 2.29 s ✓ -16.4 %                  |

| 2          | Off     | 1854      | 1229        | 9.65 s                              |

|            | On      | 430       | 386         | 5.26 s <b>-45.5</b> %               |

| 3          | Off     | 2724      | 1795        | 13.34s                              |

|            | On      | 590       | 534         | 6.56 s -50.8 %                      |

| 4          | Off     | 3594      | 2361        | 15.68 s                             |

|            | On      | 750       | 682         | 9.24s <b>-41.1%</b>                 |

WatwaOS

## **Evaluation: Optimization Time (1)**

| Interrupts | Merging | Variables | Constraints | Solving time (first 3000 scenarios) |

|------------|---------|-----------|-------------|-------------------------------------|

| 0          | Off     | 98        | 87          | 0.10 s                              |

|            | On      | 98        | 87          | 0.10 s                              |

| 1          | Off     | 984       | 663         | 2.74s                               |

|            | On      | 270       | 238         | ■ 2.29 s                            |

| 2          | Off     | 1854      | 1229        | 9.65 s                              |

|            | On      | 430       | 386         | 5.26 s <b>-45.5</b> %               |

| 3          | Off     | 2724      | 1795        | 13.34 s                             |

|            | On      | 590       | 534         | 6.56 s <b>-50.8</b> %               |

| 4          | Off     | 3594      | 2361        | 15.68 s                             |

|            | On      | 750       | 682         | 9.24s <b>-41.1%</b>                 |

✓ Up to 50 % solving time reduction by exploiting similarities in the PSTG

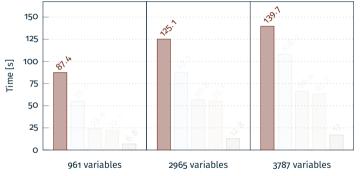

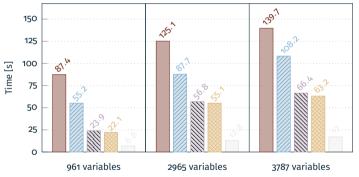

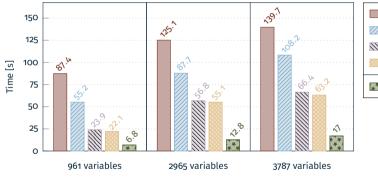

### **Evaluation: Optimization Time (2)**

### **Evaluation: Optimization Time (2)**

#### **Evaluation: Optimization Time (2)**

✓ Significant optimization time reduction by optimizing the ILP solving process

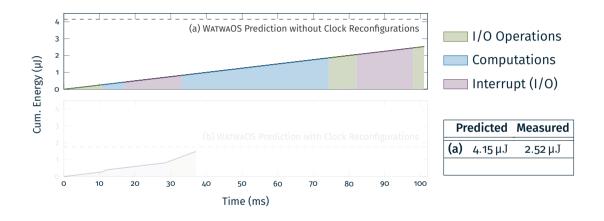

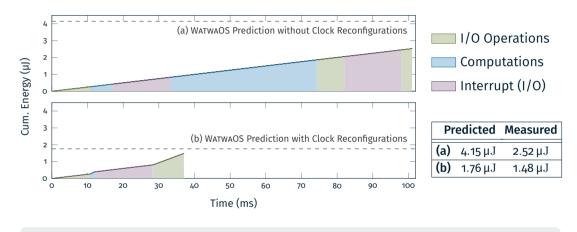

### **Evaluation: Application Example**

### **Evaluation: Application Example**

✓ Improved energy efficiency compared to static clock configuration

WatwaOS 17

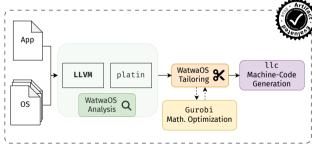

#### **WATWAOS**

$\,\rightarrow\,$  Integrated into the LLVM compiler framework

#### **WATWAOS**

- ✓ Whole-system analysis and optimization framework

- → Integrated into the LLVM compiler framework

- ✓ Minimizes energy consumption while providing safe WCET/WCEC bounds

- → Construction of a Power-State-Transition Graph with reconfiguration nodes

#### **WATWAOS**

- ✓ Whole-system analysis and optimization framework

- ightarrow Integrated into the LLVM compiler framework

- ✓ Minimizes energy consumption while providing safe WCET/WCEC bounds

- → Construction of a Power-State-Transition Graph with reconfiguration nodes

- ✓ Achieves reasonable analysis and optimization times

- → Node merging and multi-scenario ILPs

#### **WATWAOS**

- ✓ Whole-system analysis and optimization framework

- → Integrated into the LLVM compiler framework

- ✓ Minimizes energy consumption while providing safe WCET/WCEC bounds

- → Construction of a Power-State-Transition Graph with reconfiguration nodes

- ✓ Achieves reasonable analysis and optimization times

- → Node merging and multi-scenario ILPs

### WATWAOS Source Code and Artifact: